Pb-free & RoHs Product

#### **Features**

- 1200~1800MHz Frequency Range

- 30dB Power Gain (Typ.)

- 38dBm Saturation Output Power

- 10dB Input Return Loss

- 3.3~5.5V Supply Voltage

- 12mA Quiescent Current

- Integrated Output Power Detector

- Integrated ESD Protection Unit

- Advanced InGaP/GaAs HBT Technology

#### VCCD VCCB PDET 16 20 19 18 17 RF OUT NC 1 15 (VCC3) NC 2 14 **RF OUT** ぼ RF IN 3 13 **RF OUT** 4 12 NC **RF OUT Active Bias** 5 11 NC RF OUT 8 VR1&2 **VCTR**

**Functional Block Diagram**

### **Applications**

- BDS Satellite Communication and Navigation

- Unmanned Aerial Vehicle System

- 1.4GHz Drone Image Transmission

# **Product Description**

The YP163038-H is a high-power, high-efficiency Power Amplifier optimized for the applications in bands from 1200MHz to 1800MHz (it needs different matching circuit for different frequency range), such as BDS Satellite Communication and 1.4GHz Drone Image Transmission. The Power Amplifier provides a typical power gain of 30dB and saturation power of 38dBm with CW input, typical quiescent bias condition is 5.0V at 12mA. The device is manufactured on an advanced InGaP/GaAs Heterojunction Bipolar Transistor (HBT) process. The YP163038-H is assembled in a 20-pin, 5mm×5mm, QFN package, it is internally integrated with ESD protection unit.

# **Ordering Information**

■ YP163038-H 1.6GHz Power Amplifier Chip

■ YP163038-H-EVB YP163038-H Evaluation Board of 1.4GHz, 1.6GHz

### 1200-1800MHz 6W GaAs MMIC Power Amplifier

# **Pin Description**

| Pin No.            | Symbol        | Description                                                         |  |

|--------------------|---------------|---------------------------------------------------------------------|--|

| 3                  | RF IN         | RF input                                                            |  |

| 7, 9               | VR1&2, VR3    | Bias current control voltage                                        |  |

| 11, 12, 13, 14, 15 | RF OUT (VCC3) | RF output and Supply voltage for stage 3                            |  |

| 16                 | VCC2          | Supply voltage for stage 2                                          |  |

| 17                 | PDET          | Power detect                                                        |  |

| 18                 | VCCB          | Supply voltage for bias                                             |  |

| 19                 | VCCD          | Supply voltage for power detector                                   |  |

| 20                 | VCC1          | Supply voltage for stage 1e                                         |  |

| 1, 2, 4, 5, 6, 10  | NC/GND        | No connection or ground                                             |  |

|                    |               | Power on/off control voltage. Apply >2.5VDC to power down the three |  |

| 8                  | VCTR          | power amplifier stages. Apply 0VDC to power up. If function is not  |  |

|                    |               | desired, pin8 may be connected to GND                               |  |

| PKG Base           | GND           | Ground connection                                                   |  |

# **Absolute Maximum Ratings**

| Parameter           | Symbol          | Rating        | Unit |

|---------------------|-----------------|---------------|------|

| Input RF Power      | RF IN           | +10           | dBm  |

| Supply Voltage      | VCC1,VCC2,VCC3, | 0.E.to. 1.6.0 | V    |

| Supply Voltage      | VCCB,VCCD       | -0.5 to +6.0  |      |

| Reference Voltage   | VR1&2, VR3      | -0.5 to +3.0  | V    |

| Operating Ambient   | т               | -40 to +105   | °C   |

| Temperature         | T <sub>OP</sub> | -40 10 + 105  |      |

| Storage Temperature | T <sub>ST</sub> | -40 to +150   | °C   |

### Caution! ESD Sensitive Device.

ESD Rating: Class1C

Value: Passes≥1000V min.

Test: Human Body Model (HBM)

Standard: JEDEC Standard JESD22-A114

ESD Rating: Class IV

Value: Passes ≥1000V min.

Test: Charged Device Model (CDM)

Standard: JEDEC Standard JESD22-C101

MSL Rating: Level 3 at +260 °C convection reflow Standard: JEDEC Standard J-STD-020

# **Electrical Specifications**

| Parameter               | Specification |      | Unit | Condition |                                    |  |

|-------------------------|---------------|------|------|-----------|------------------------------------|--|

| Farailletei             | Min.          | Тур. | Max. | Offic     | Condition                          |  |

| Compliance and          |               |      |      |           | VCC1=VCC2=VCC3=VCCB=5.0V,          |  |

| Nominal Conditions      |               |      |      |           | ICQ=12mA, T <sub>OP</sub> =+25°C   |  |

| Frequency range         |               | 1615 |      | MHz       |                                    |  |

| Saturation output power |               | 38.3 |      | dBm       | Pulse Mode: Period=1s, Width=300ms |  |

| Power gain              |               | 30.0 |      | dB        | @Pout=38.3dBm                      |  |

| Input return loss       |               | 10.0 |      | dB        |                                    |  |

| Reference Voltage       |               | 2.4  |      | V         |                                    |  |

| Quiescent current, ICQ  |               | 12   |      | mA        | VR1&2=VR3=2.4V                     |  |

| Operating current, ICC  |               | 2920 |      | mA        | @Pout=38.3dBm                      |  |

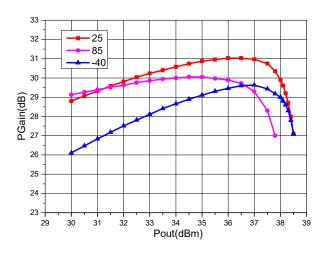

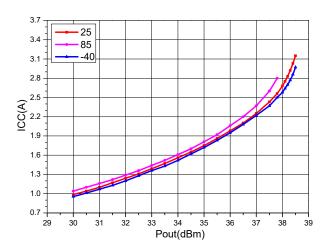

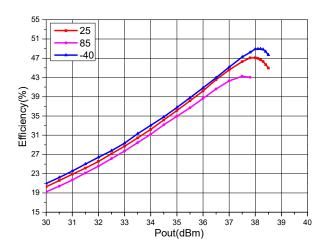

# **Typical Performance**

(Test Condition: Freq=1615MHz, VCC1=VCC2=VCC3=VCCB=5V, VR1&2=VR3=2.4V, T<sub>OP</sub>=+25°C)

### PGain vs. Output Power

ICC vs. Output Power

Efficiency vs. Output Power

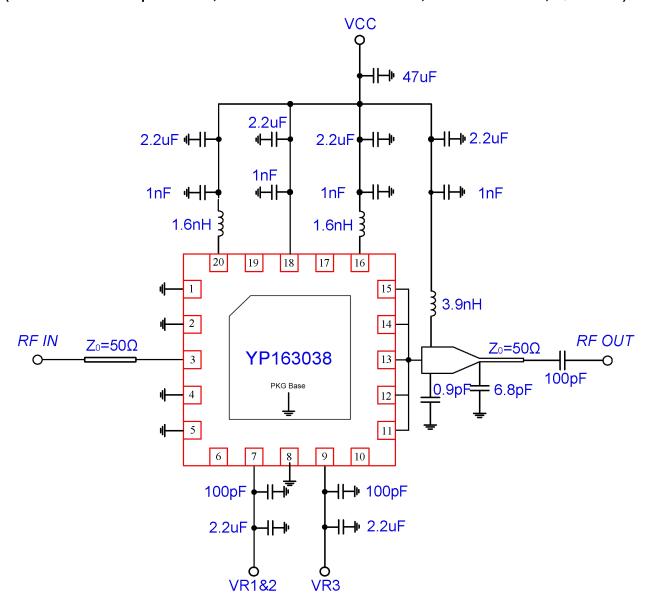

### **Evaluation Board Schematic**

(Test Condition: Freq=1615MHz, VCC1=VCC2=VCC3=VCCB=5V, VR1&2=VR3=2.4V, T<sub>OP</sub>=+25°C)

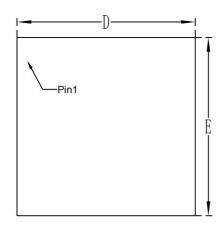

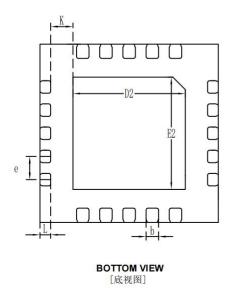

# **Packaging Diagram**

| 编号 | 尺寸 (mm)     |        |        |  |  |

|----|-------------|--------|--------|--|--|

| 洲与 | Min         | TYP    | Max    |  |  |

| A  | 0.650       | 0.750  | 0.850  |  |  |

| A1 | 0.000       | 0.020  | 0.050  |  |  |

| A3 | Ī           | 0.203  |        |  |  |

| b  | 0.300       | 0.350  | 0.400  |  |  |

| D  | 4.900       | 5.000  | 5. 100 |  |  |

| Е  | 4.900       | 5.000  | 5. 100 |  |  |

| е  | I           | 0.650  | 1      |  |  |

| D2 | <del></del> | 3. 150 | 2.——   |  |  |

| E2 | 1           | 3. 150 | 1      |  |  |

| L  | I           | 0.300  | l      |  |  |

| K  | 0.200       | 0.625  | :      |  |  |

| R  | 0.090       | 0. 125 |        |  |  |

|    |             |        |        |  |  |

|    |             |        |        |  |  |

|    |             |        |        |  |  |

### Note 1

Vias(Φ0.3mm THRU \* 25) are required under the backside paddle of this device for proper RF/DC grounding and thermal dissipation. ALL vias are PTH to ground.

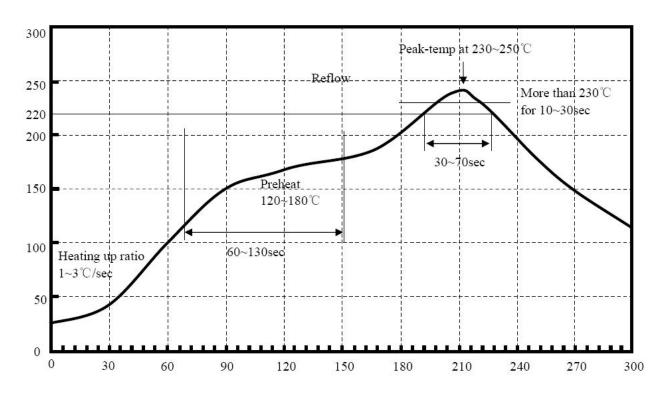

## **Recommended Solder Temperature**

**Recommended Temperature**

Sn95.5Ag4.0Cu0.5

### Note 2

If these amplifiers are to be subjected to solder reflow or high temperature processes, they must be baked for 48 hours at 125°C prior to board mount. Failure to comply may result in crack and/or delamination of critical interfaces within the package.